# TI-99/4A CONSOLE AND PERIPHERAL EXPANSION SYSTEM TECHNICAL DATA

Texas Instruments Home Computer

TI-99/4A CONSOLE

AND

PERIPHERAL EXPANSION SYSTEM

TECHNICAL DATA

Copyright 1983 Texas Instruments Incorporated

# TABLE OF CONTENTS

# Section A--TI-99/4A CONSOLE

| A.1             | General Description5                              |

|-----------------|---------------------------------------------------|

| A.2             | I/O Pin Description7                              |

| A.3             | Memory Allocation9                                |

| A.4             | LRU Allocation10                                  |

| A.5<br>A.6      | Interrupt Handling                                |

| A.0             | Electrical Characteristics12                      |

| FIGURE          | IllustrationsSection A                            |

| A               | TI-99/4A System Block Diagram6                    |

| В .             | I/O READ Timing                                   |

| C               | I/O WRITE Timing                                  |

| D               | CRU Timing                                        |

| Ε               | Connector Pin Identification Diagram              |

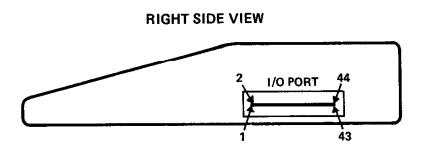

| F               | TI-99/4A Logic Board Component Location Diagram19 |

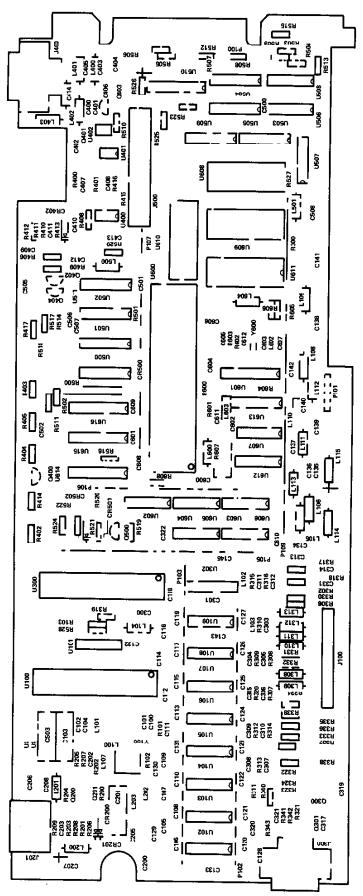

| G               | TI-99/4A Power Supply20                           |

|                 | Section BINTERFACE CONSIDERATIONS                 |

| B.1CPU Requi    | rements                                           |

|                 | eral Comments21                                   |

| B.1.2 TI-       | 99/4A Memory Space Organization21                 |

| 8.1.2           | .1 READ before WRITE considerations22             |

| B.1.2           | .2 Cartridge Memory Space22                       |

| B.1.3 CRU       | Space Definition24                                |

| B.1.3           | .1 Disallowed Instructions24                      |

| B.1.3           | .2 CRU OUTPUT Definition24                        |

| B.1.3           | .3 CRU INPUT Definition24                         |

| B.1.3           |                                                   |

| B.1.4 TI-       | 99/4A Peripheral Polling27                        |

| 8.1.5 Ind       | icator LED27                                      |

| B.1.6 DSR       | ROM Considerations27                              |

| B.1.6           | .1 Extended DSR ROM Techniques27                  |

| B.2—Expansion   | Unit Requirements                                 |

| B.2.1 Sys       | tem Bus Requirements27                            |

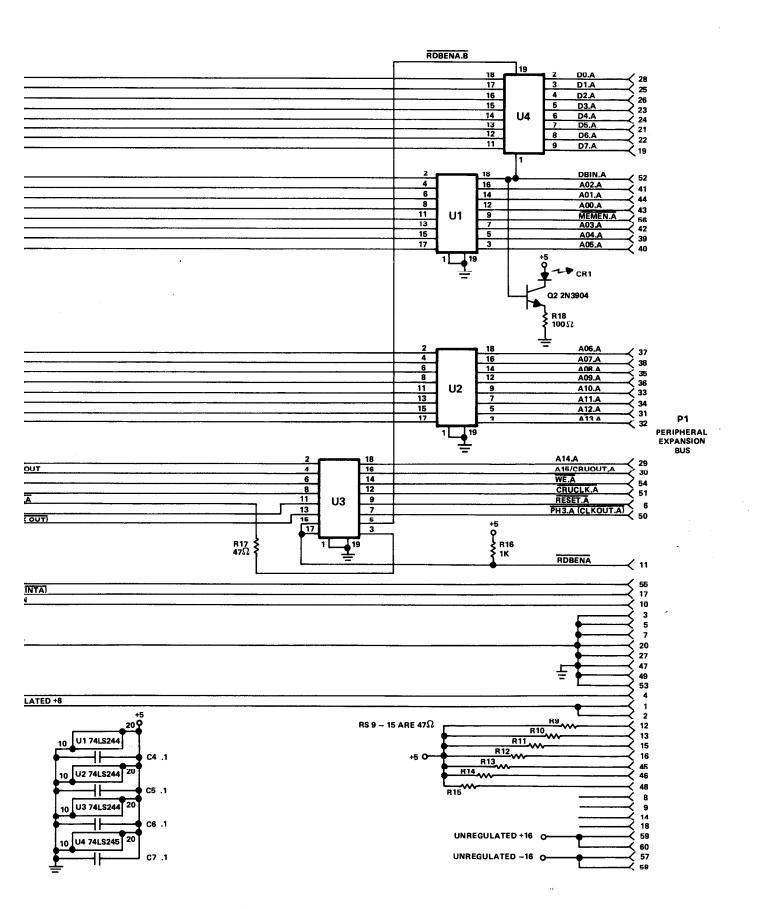

| B.2.1           | .1 Remote Data Bus Driver28                       |

| B.2.1           | .2 Burn-In Consideration28                        |

| B.2.2 Pow       | er Allocation Assumptions28                       |

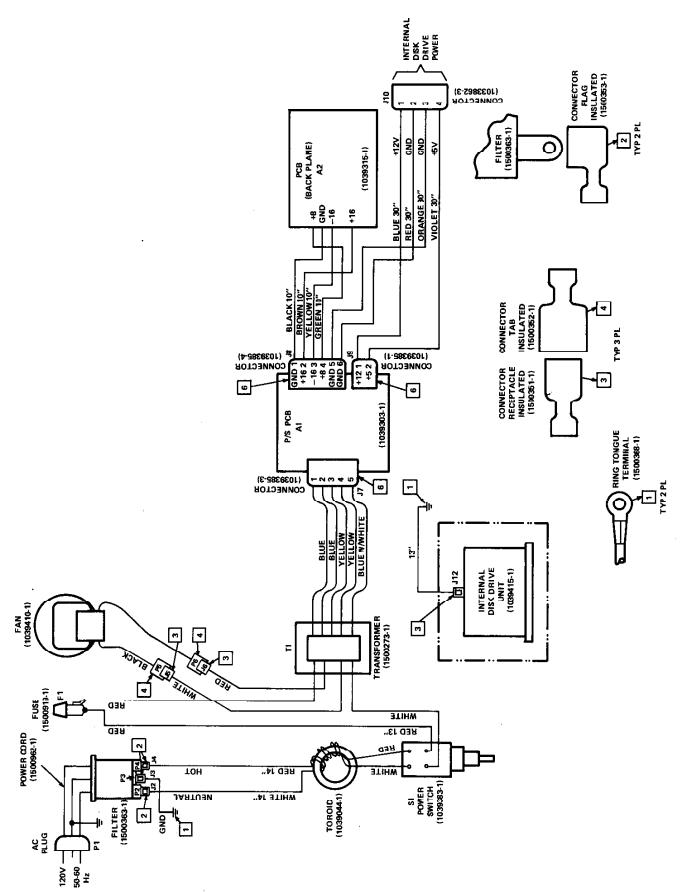

| B.2.3 Sys       | tem Bus Pin Definition29                          |

| B.3——Design and | d Development Requirements31                      |

|                 | IllustrationsSection B                            |

| TI_00/4/\ Momow | y Map23                                           |

| CRU Man         | у мар23<br>•••••••25–26                           |

| Peripheral Exp. | ansion Unit Schematic Diagram                     |

|                 |                                                   |

# Section C--FILE MANAGEMENT SPECIFICATIONS

| C.1 Introduction33                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C.2 I/O Handling       34         C.2.1 File Organization and Use       34         C.2.1.1 Sequential Files       34         C.2.1.2 Relative Record Files       34         C.2.2 File Management Overview       35         C.2.2.1 Terminology       35         C.2.2.2 File-Type Attribute       36         C.2.2.3 Mode of Operation       36         C.2.2.4 Temporary Files       36 |

| C.3 Implementation. 37 C.3.1 Peripheral Access Block Definition. 37 C.3.2 I/O Opcodes. 39 C.3.2.1 OPFN. 40 C.3.2.2 CLOSE. 40 C.3.2.3 READ. 40 C.3.2.4 WRITE. 41 C.3.2.5 RESTORE/REWIND. 41 C.3.2.6 LOAD. 41 C.3.2.7 SAVE. 41 C.3.2.8 DELETE. 42 C.3.2.9 SCRATCH RECORD. 42 C.3.2.10 STATUS. 42 C.3.3 Error Codes. 43                                                                      |

| C.4 DSR Operations                                                                                                                                                                                                                                                                                                                                                                        |

| C.5 Linkage to BASIC                                                                                                                                                                                                                                                                                                                                                                      |

| C.3.1.1 PAB Layout                                                                                                                                                                                                                                                                                                                                                                        |

# Section D--DEVICE SERVICE ROUTINE SPECIFICATIONS

|                |                        | uction<br>General Interface                                                                                                         |                      |             |                |

|----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|----------------|

|                |                        | s                                                                                                                                   |                      |             |                |

|                | Hardwa<br>.3.1<br>.3.2 | re Structure of DSR<br>DSR ROM<br>CRU Mapping                                                                                       |                      |             | 51             |

| []<br>[]<br>[] |                        | re Structure of DSR Symbol Definition Block Header and Linkage Block. A Sample Program for Heade Power-up Routine Interrupt Routine | er and Linkage Block |             | 52<br>53<br>54 |

| GI C           | SSARY                  |                                                                                                                                     |                      | • • • • • • | 57             |

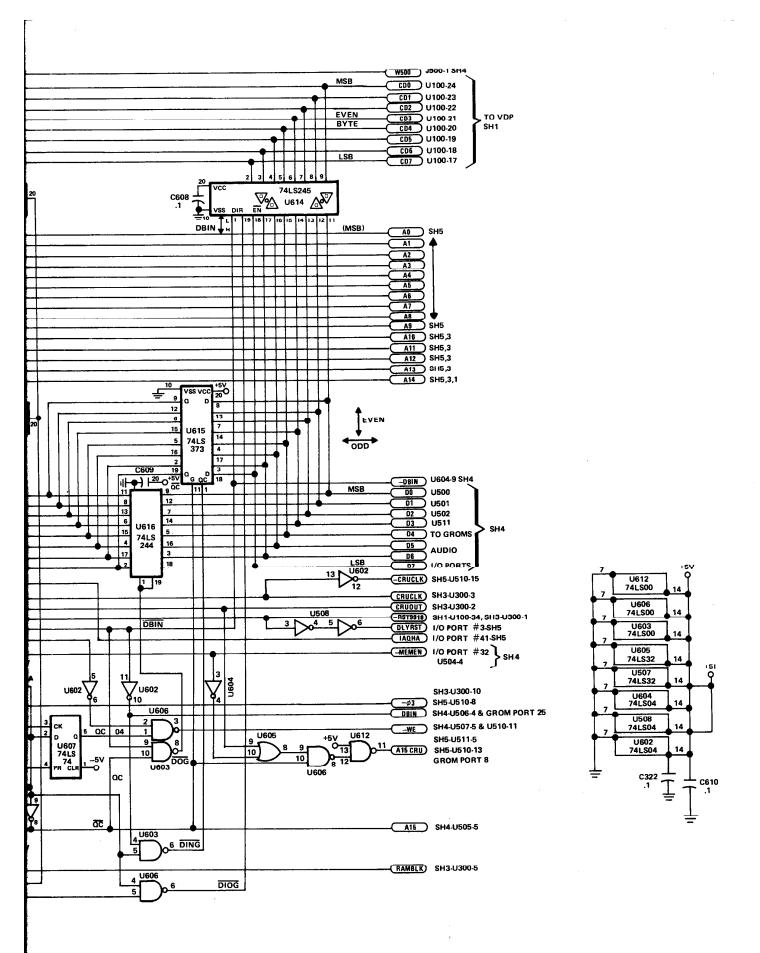

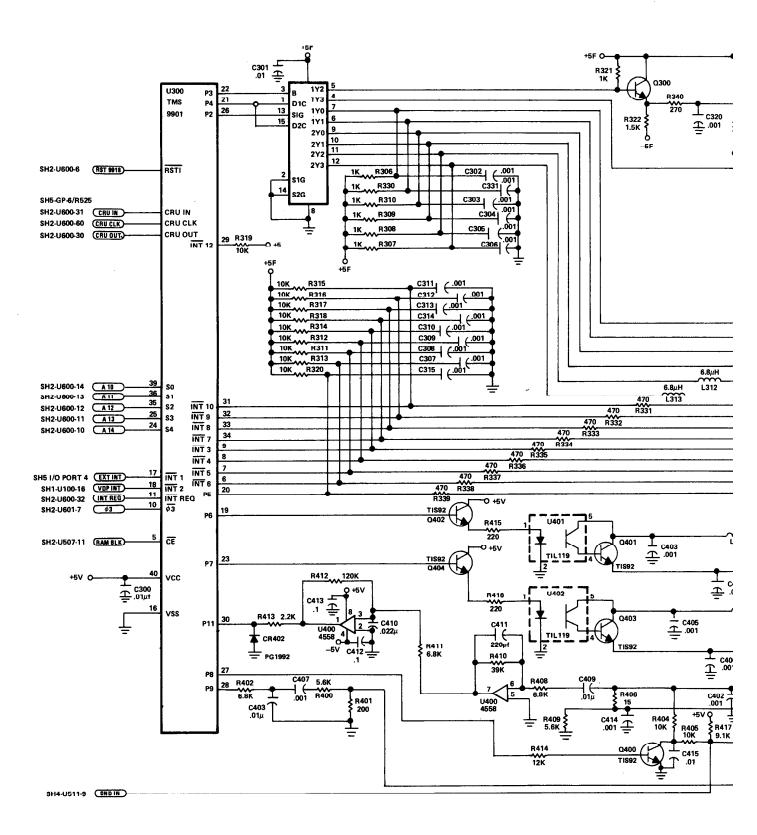

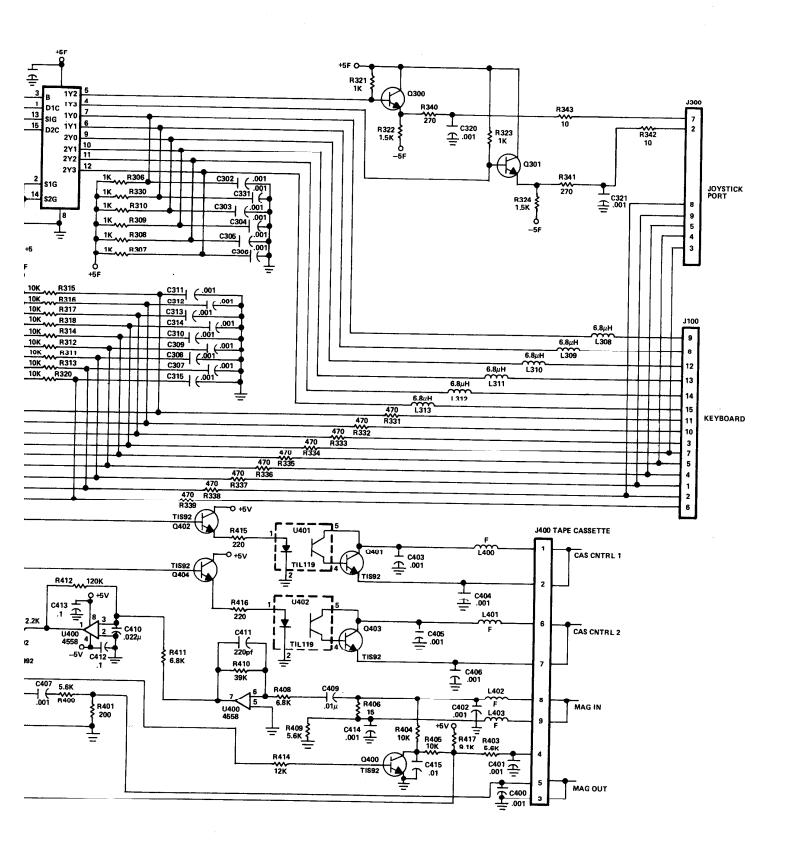

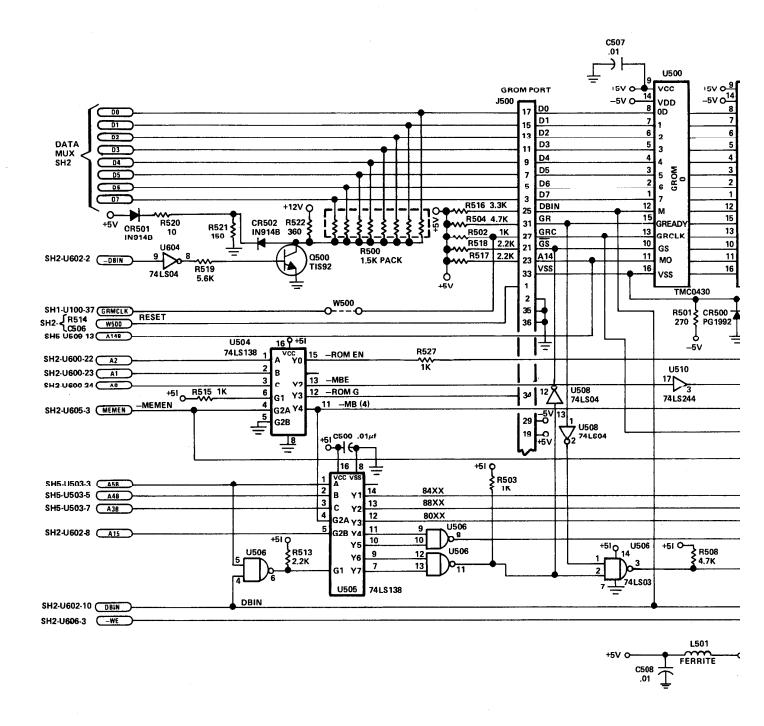

| APF            | ENDIXF                 | old-out Schematic Diagrams                                                                                                          |                      |             |                |

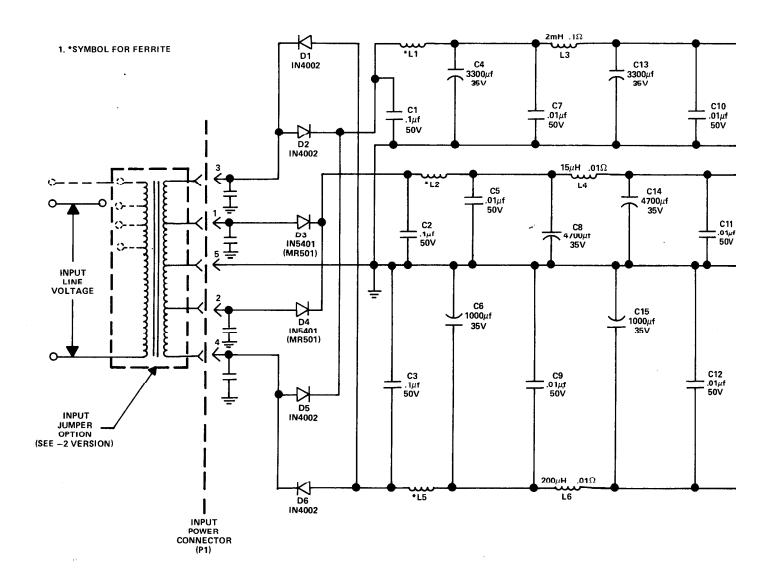

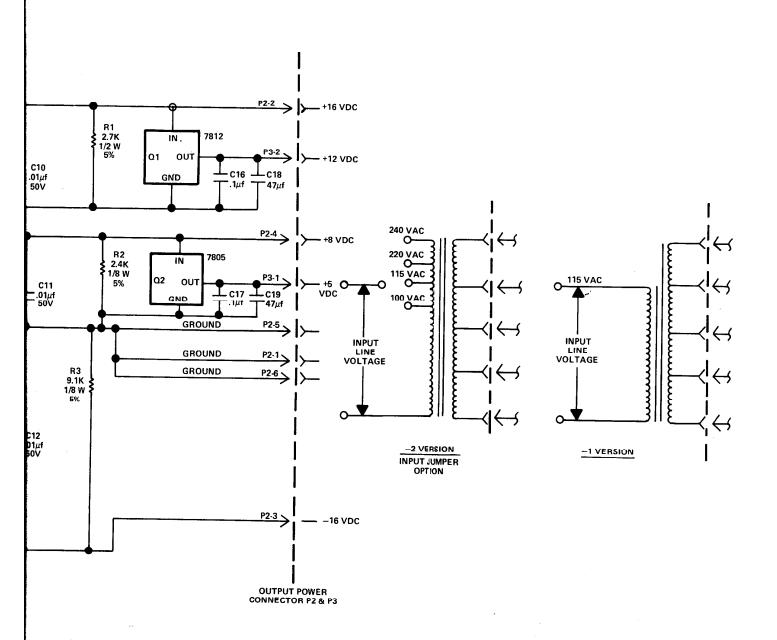

|                | Flex C                 | 4A Schematic Diagrams (5 pable I/O Schematic Diagram<br>eral Expansion Unit Power                                                   | s (2 pages)          |             | 64-65          |

|                |                        |                                                                                                                                     |                      |             |                |

# SECTION A TI-99/4A CONSOLE

# A.1 GENERAL DESCRIPTION

The purpose of this section is to provide necessary information concerning the I/O bus (input/output signal connection) of the TI-99/4A console for persons interested in designing peripherals for the computer.

It is assumed that readers of this manual have a working knowledge of electronics and computers, especially in regard to the TMS 9900 microprocessor and its Communications Register Unit (CRU) I/O technique. Sources for this information are the TMS9900 Microprocessor Data Manual (MPOO1, Revision A) or the TMS9901 Programmable Systems Interface (MPOO3; July, 1978). These books may be obtained from TI semiconductor distributors or the TI Learning Center. A glossary is provided on page 57 of this manual.

The I/O bus provides an interface between the console and its peripherals. This bus utilizes both memory-mapped I/O and CRU I/O. The memory bus is frequently used for instruction fetch from read-only memory (ROM) in external peripherals and for data transfer to and from memory-mapped portions of these devices. The CRU bus is used for peripheral enable/disable, device control, and data transfer to/from CRU-mapped portions of these peripherals.

The TMS 9900 microprocessor accesses each peripheral to obtain instructions from the device service routine (DSR) ROM. Since each peripheral contains its own DSR, the TI-99/4A does not have to be designed to anticipate future peripheral requirements. The dual I/O bus capability, interrupt handling, and external DSRs provide flexibility at low cost.

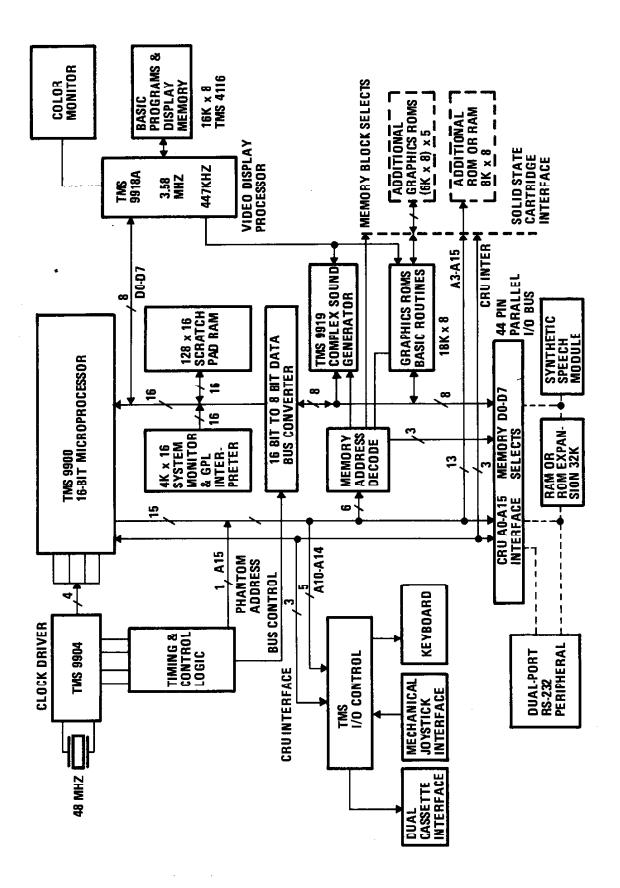

FIGURE A. TI-99/4A SYSTEM BLOCK DIAGRAM

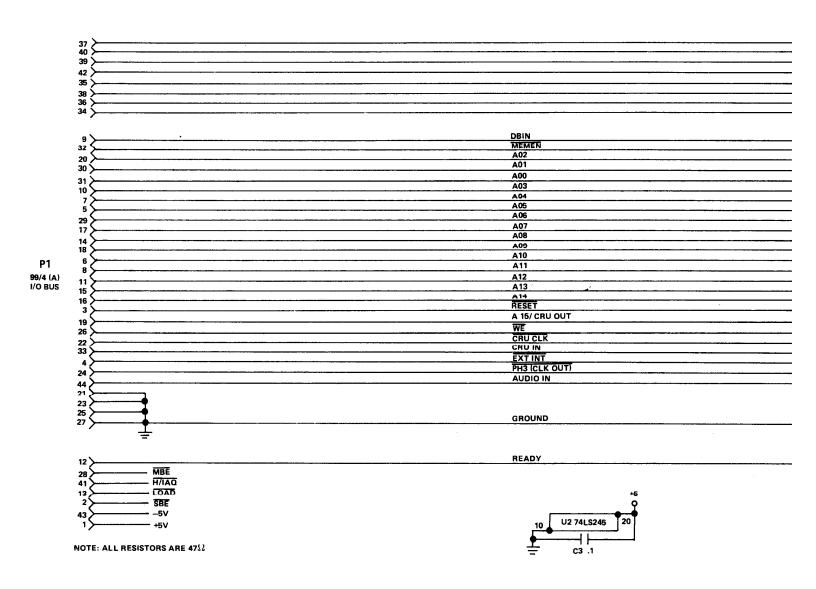

| A.2 I/O PIN D<br>SIGNATURE                                         | DESCRIPTION PIN                                                                    | ON<br>I/O                                     | DESCRIPTION                                                                                                                                                                                                                           |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AO (MSB) A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15/CRUOUT | 31<br>30<br>20<br>10<br>7<br>5<br>29<br>17<br>14<br>18<br>6<br>8<br>11<br>15<br>16 | Out       | ADDRESS BUS  AO through A15 comprise the address bus. This bus provides the 16-bit memory address vector to the external memory system when MEMEN is active. Address bit 15 is also used for CRU DATA OUT on CRU output instructions. |

| DO (MSB) D1 D2 D3 D4 D5 D6                                         | 37<br>40<br>39<br>42<br>35<br>38<br>36<br>34                                       | I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0<br>I/0 | DATA BUS  DO through D7 comprise the bidirectional data bus. This bus transfers memory data to (when writing) and from (when reading) the external memory system when MEMEN is active.                                                |

|                                                                    |                                                                                    |                                               | BUS CONTROL                                                                                                                                                                                                                           |

| MEMEN                                                              | 32                                                                                 | Out                                           | MEMory ENable. MEMEN indicates a memory access.                                                                                                                                                                                       |

| DBIN                                                               | 9                                                                                  | Out                                           | Data Bus IN. When active (high) the data buffers and 9900 are in the input mode.                                                                                                                                                      |

| WE                                                                 | 26                                                                                 | Out.                                          | Write Enable. WE indicates a memory write.                                                                                                                                                                                            |

| MBE                                                                | 28                                                                                 | Out                                           | Memory Block Enable. MBE indicates a memory access in memory block 4000-5FFF.                                                                                                                                                         |

| CRUCLK                                                             | 22                                                                                 | Out                                           | CRU CLock. Input data line to the Home Computer.                                                                                                                                                                                      |

| CRUIN                                                              | 33                                                                                 | In                                            | CRU data IN. Input data line to the Home Computer.                                                                                                                                                                                    |

# I/O PIN DESCRIPTION (CONTINUED)

| SIGNATURE      | PIN            | <u>I/0</u> | DESCRIPTION                                                                                                                                                 |

|----------------|----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                |            | MEMORY CONTROL                                                                                                                                              |

| READY          | 12             | In         | READY (when $\overline{\text{MEMEN}}$ is active) indicates external memory is ready for a memory access.                                                    |

| IAQ            | 41             | Out        | Instruction AcQuisition indicates the CPU is acquiring an instruction during the current memory cycle.                                                      |

|                |                |            | TIMING AND CONTROL                                                                                                                                          |

| LOAD           | 13             | In         | When active, LOAD causes the CPU to execute a nonmaskable interrupt; memory addresses FFFC and FFFE contain the new workspace and PC vectors, respectively. |

| RESET          | 3              | Out        | When active, RESET causes the Home Computer and the peripherals to be reset. RESET will be held active for a minimum of five clock cycles.                  |

| EXT INT        | 4              | In         | EXTernal INTerrupt. When active, EXT INT causes the CPU to execute an interrupt.                                                                            |

| <del>ø</del> 3 | 24             | Out        | CPU Clock. Phase 3 of the CPU clock.                                                                                                                        |

|                |                |            | POWER                                                                                                                                                       |

| GND            | 21,23<br>25,27 |            | Ground reference.                                                                                                                                           |

|                |                |            | SPEECH MODULE SIGNALS                                                                                                                                       |

| SBE            | 2              | 0ut        | Speech Block Enable. SBE indicates a memory access in the speech memory.                                                                                    |

| AUDIO IN<br>+5 | 44<br>1        | In         | Input for the audio from the speech module Supply voltage (+5v Nom) for speech module (50ma Max)*                                                           |

| -5             | 43             |            | Supply voltage (-5v Nom) for speech module (50ma Max)*                                                                                                      |

$<sup>\</sup>mbox{*}$  NOTE: Pins 1 and 43 are not intended for use by consumer. Overload may cause permanent damage to console.

# A.3 MEMORY ALLOCATION

The memory address space is broken into eight blocks of 8K bytes of memory. The third block (addresses 4000-5FFF) is predecoded and made available at the I/O port for the peripherals. The second, sixth, seventh, and eighth blocks (addresses 2000-3FFF and 4000-FFFF) are in the Memory Expansion peripheral. For the speech module (addresses 9000-97FF), a predecoded line is available at the I/O port.

# SYSTEM MEMORY MAP

#### HEX ADDRESS

| 0-1FFF      | Console ROM space                                       |

|-------------|---------------------------------------------------------|

| 2000-3FFF · | Memory Expansion Peripheral                             |

| 4000-5FFF   | Peripheral Expansion (predecoded to I/O connector)      |

| 6000-7FFF   | Cartridge ROM/RAM (predecoded to GROM connector)        |

| 8000-9FFF   | Microprocessor ROM, VDP, GROM, SOUND and SPEECH select. |

| A000-BFFF   | Memory Expansion peripheral                             |

| COOO-DFFF   | Memory Expansion peripheral                             |

| E000-FFFF   | Memory Expansion peripheral                             |

# MEMORY-MAPPED DEVICES

| <u>ADDRESSES</u> | <u>A0</u> | A1 | A2 | А3 | Α4 | A5 | A14 | USE               |

|------------------|-----------|----|----|----|----|----|-----|-------------------|

| 8000             | 1         | 0  | 0  | 0  | 0  | 0  | 0   | Internal RAM      |

| 0400             | _         | _  | _  | _  |    |    |     | (8300-83FF)       |

| 8400             | 1         | 0  | 0  | 0  | 0  | 1  | 0   | Sound             |

| 8800             | 1         | 0  | 0  | 0  | 1  | 0  | 0   | VDP Read Data     |

| 8802             | 1         | 0  | 0  | 0  | 1  | 0  | 1   | VDP Read Status   |

| 0008             | 1         | 0  | 0  | 0  | 1  | 1  | 0   | VDP Write Data    |

| 8C02             | 1         | 0  | 0  | 0  | 1  | 1  | 1   | VDP Write Address |

| 9000             | 1         | 0  | 0  | 1  | 0  | 0  | 0   | Speech Read       |

| 9400             | 1         | 0  | 0  | 1  | 0  | 1  | Ō   | Speech Write      |

| 9800             | 1         | 0  | Ò  | 1  | 1  | ō  | Ö   | GROM Read Data    |

| 9802             | 1         | 0  | 0  | 1  | ĩ  | Õ  | ĭ   | GROM Read Address |

| 9C00             | 1         | 0  | Ö  | 1  | ī  | ĭ  | ñ   | GROM Write Data   |

| 9C02             | 1         | Ö  | Ö  | ī  | ī  | ī  | ĭ   | GROM Write Data   |

NOTE: Memory-mapped devices at addresses >8000 through >9FFF are only partially decoded. Thus, the devices will respond not only at the base addresses listed above, but also at other addresses within the 1K block. For more information, see Section B.1 on page 25.

## A.4 CRU ALLOCATION

Of the available 4K of CRU bits, the first 1K (addresses 0000-07FE) are used internally in the console. The second 1K (addresses 0800-0FFE) are reserved for future use. The last 1.9K (addresses 1000-1FFE) are reserved for the peripherals to be plugged in the I/O port. A block of 128 CRU bits is assigned to each peripheral as listed below.

## CRU ASSIGNMENTS

| CRU<br>ADDRESSES | A3 | A4 | A5 | A6 | A7 | USE                      |

|------------------|----|----|----|----|----|--------------------------|

| 0000-0FFE        | 0  | Χ  | Χ  | Χ  | χ  | Internal Use             |

| 1000-10FE        | 1  | 0  | 0  | 0  | 0  | Unassigned               |

| 1100-11FE        | 1  | 0  | 0  | 0  | 1  | Disk Controller Card     |

| 1200-12FE        | 1  | 0  | 0  | 1  | 0  | Modems                   |

| 1300-13FE        | 1  | 0  | 0  | 1  | 1  | RS 232 (primary)         |

| 1400-14FE        | 1  | 0  | 1  | 0  | 0  | Unassigned               |

| 1500-15FE        | 1  | 0  | 1  | 0  | 1  | RS 232 (secondary)       |

| 1600-16FE        | 1  | 0  | 1  | 1  | 0  | Unassigned               |

| 1700-17FE        | 1  | 0  | 1  | 1  | 1  | HE X-BUŠTM               |

| 1800-18FE        | 1  | 1  | 0  | 0  | 0  | Thermal Printer          |

| 1900-1FFE        | 1  | 1  | 0  | 0  | 0  | EPROM Programmer         |

| 1A00-1AFE        | 1  | 1  | 0  | 1  | 0  | Unassigned               |

| 1B00-1BFE        | 1  | 1  | 0  | 1  | 1  | Unassigned               |

| 1COO-1CFE        | 1  | 1  | 1  | 0  | 0  | Video Controller Card    |

| 1000-1DFE        | 1  | 1  | 1  | 0  | 1  | IEEE 488 Controller Card |

| 1E00-1EFE        | 1  | 1  | 1  | 1  | 0  | Unassigned               |

| 1F00-1FFE        | 1  | 1  | 1  | 1  | 1  | P-Code Card              |

# A.5 INTERRUPT HANDLING

The interrupt available on the I/O port is one of the maskable interrupts of the TMS 9901 Programmable Systems Interface.

## 9900 INTERRUPTS

| INTERRUPT<br>LEVEL<br>(Highest | VECTOR LOC.<br>(MEMORY ADDR.<br>IN HEX)<br>0000-WSP | CPU<br>PIN<br>RESET                     | DEVICE<br>ASSIGNMENT<br>RESET           |

|--------------------------------|-----------------------------------------------------|-----------------------------------------|-----------------------------------------|

| Priority)                      | 0002-PC                                             | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| 0                              | FFFC-WSP<br>FFFE-PC                                 | LOAD                                    | LOAD                                    |

| 1                              | 0004-WSP<br>0006-PC                                 |                                         | EXT DEV (9901)                          |

Interrupting is done only on Level 1. The additional interrupts available are implemented on 9901. Interrupt Level 1 is decoded by software to be either (1) VDP vertical sync., (2) 9901 internal timer, or (3) I/O bus generated.

| ADDRESS      | CRU BIT       | 9901 BIT (<br>9901                | ORGANIZAT.<br>PIN |                                            |

|--------------|---------------|-----------------------------------|-------------------|--------------------------------------------|

|              |               | 3501                              | 1.11              | FUNCTION                                   |

| 0000         | 0             | Control                           |                   | Control                                    |

| 0002         | 1             | <u>INTI</u>                       | 17                | External Interrupt                         |

| 0004         | 2             | INT2                              | 18                | Video Display Processor                    |

| 0000         | •             |                                   |                   | Vertical Sync Interrupt                    |

| 0006         | 3             | INT3                              | 9                 | 9901 Internal Timer Interrupt,             |

|              |               |                                   |                   | keyboard "=" line,                         |

| 8000         | 4             | INT4                              |                   | joystick "FIRE"                            |

| 0000         | 4             | IN 14                             | 8                 | Keyboard "Space" line,                     |

| 000A         | 5.            | INT5                              | 7                 | joystick "Left"                            |

|              | •             | 11110                             | ,                 | Keyboard "ENTER" line,<br>joystick "Right" |

| 000C .       | 6             | INT6                              | 6                 | Keyboard "O" line,                         |

|              |               |                                   | •                 | joystick "Down"                            |

| 000E         | 7             | ĪNT7 (P15)                        | 34                | Keyboard "FCTN" line.                      |

| 0010         | _             |                                   |                   | joystick "Up"                              |

| 0010<br>0012 | 8<br><b>9</b> | INT8 (P14)                        | 33                | Keyboard "SHIFT" line                      |

| 0014         |               | <u>INT9</u> (P13)                 | 32                | Keyboard "CTRL" line                       |

| 0016         | 10            | <u>INT10</u> (P12)                | 31                | Keyboard "Z" line                          |

| 0018         | 11<br>12      | INT11 (P11)                       | 30                | Not Used As Interrupt                      |

| 001A-1E      | 13–15         | <u>INT12 (P10)</u><br>INT13-INT15 | 29                | Reserved, High Level                       |

| 301N-1L      | 10-10         | TM 1 T2-1M 1 T2                   | 28,27<br>and 23   | Not Used As Interrupt                      |

|              |               |                                   | anu 23            | · · · · · · · · · · · · · · · · · · ·      |

# 9901 I/O MAPPING

| ADDRESS                                              | CRU BIT                          | 9901                                                              | PIN                                    | FUNCTION                                                                                                                 |

|------------------------------------------------------|----------------------------------|-------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0020<br>0022<br>0024<br>0026<br>0028<br>002A<br>002C | 16<br>17<br>18<br>19<br>20<br>21 | PO<br>P1<br>P2<br>P3<br>P4<br>P5<br>P6                            | 38<br>37<br>26<br>22<br>21<br>20<br>19 | Reserved Reserved Bit 2 of Keyboard Select Bit 1 of Keyboard Select Bit 0 (MSB) of Keyboard Select Keyboard (ALPHA LOCK) |

| 002E                                                 | 23                               | P7 (TNT15)                                                        | 23                                     | Cassette Control 1 (motor control) Cassette Control 2 (motor control)                                                    |

| 0030<br>0032<br>0034<br>0036<br>0038–003E            | 24<br>25<br>26<br>27<br>28–31    | P8 (INT14)<br>P9 (INT13)<br>P10 (INT12)<br>P11 (INT11)<br>P12-P15 | 27<br>28<br>29<br>30<br>31–34          | Audio Gate Mag Tape Out Reserved Mag Tape Input Not Used IN I/O Mapping                                                  |

## A.6 ELECTRICAL CHARACTERISTICS

#### DRIVE CAPABILITY OF I/O SIGNALS

| SIGNAL NAME | DRIVER  |

|-------------|---------|

| <b>ø</b> 3  | 74LS244 |

| CRUCLK      | 74LS244 |

| WE          | 74LS244 |

| AO          | 74LS244 |

| A1          | 74LS244 |

| DBIN        | 74LS04  |

| MBE         | 74LS244 |

| MEMEN .     | 74LS32  |

| A3-A14      | 74LS367 |

| DO-D7       | 74LS245 |

| A15/CRUOUT  | 74LS244 |

| SBE         | 74LS03  |

| HOLD        | 74LS32  |

| RESET       | 74LS04  |

#### I/O READ

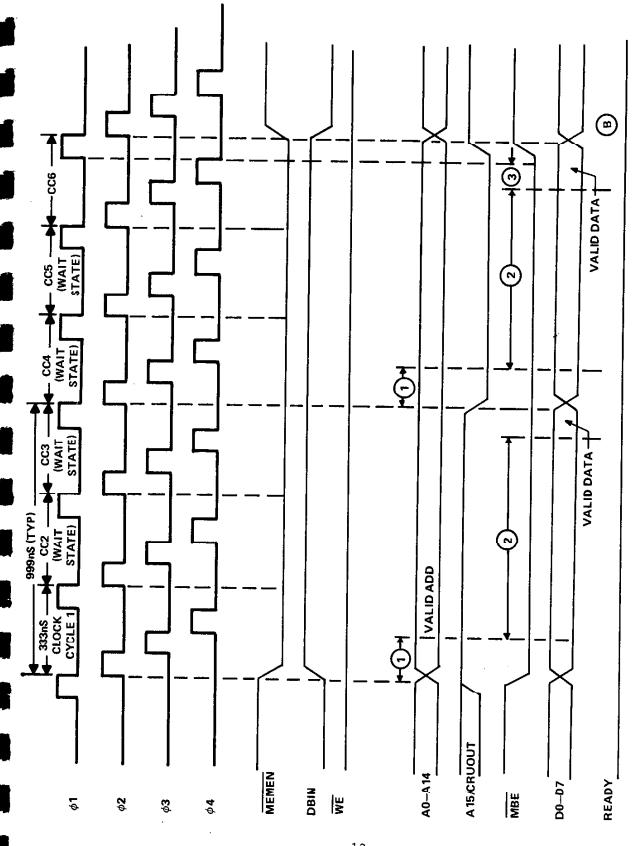

A CPU Read cycle for the external device consists of two 8-bit read cycles (Figure B). The two bytes read are assembled as a 16-bit word before they are presented to the 9900. Shown in Figure B are two 8-bit read cycles with one wait state inserted in each to work with slow memories.

At the beginning of clock cycle 1, MEMEN goes low true and DBIN goes high true. At the same time that MEMEN goes true, the address bus goes active. WE stays high false during the entire cycle.

In order to eliminate noise and glitches (associated with crosstalk and simultaneous switching), a minimum of 100 nanoseconds should be allowed for the address lines to settle. MBE (predecoded from AO, A1, and A2) goes true during the leading edge of  $\phi 2$  of clock cycle 1. Data read from the peripherals must be valid 750 nanoseconds after the start of clock cycle 1.

The CPU will look at the full 16-bit data bus during the leading edge of  $\phi 1$  of clock cycle 6. Under worst-case conditions, data must be valid 100 nanoseconds before that time.

FIGURE B. I/O READ TIMING

① SETTLING TIME = 100nS |MIN)

② ACCESS TIME FOR DSR ROM + DATA Ts + DATA BUFF DELAY (PERIPHERAL + MAINFRAME) = 650nS (MAX)

③ SETUP TIME FOR 9900 = 60nS (MIN)

# I/O WRITE

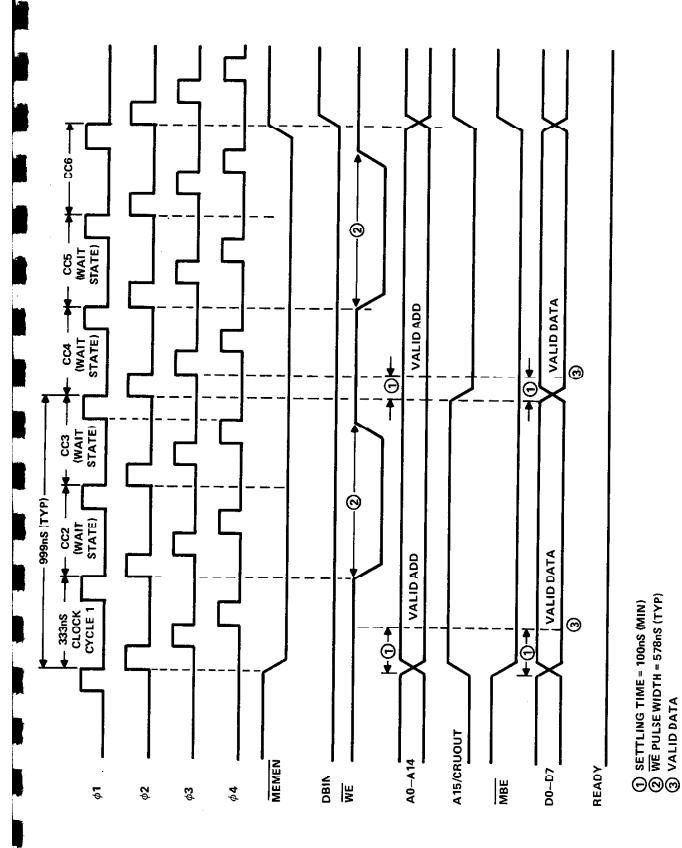

Figure C shows a 16-bit I/O write cycle. As described earlier, it is composed of two 8-bit writes. A write cycle will always be preceded by an ALU cycle.

MEMEN and DBIN go true (low) at the start of the cycle. A time of 100 nanoseconds (min) is allowed for the address lines to settle. WE goes true (low) on the leading edge of  $\phi 2$  during the wait states and stays true for 666 nanoseconds (TYP).

During a Read or a Write the odd byte (LSBY) is accessed first, then the even byte (MSBY). Al5/CRUOUT changes its state 1 microsecond (TYP) after the cycle is initiated. The second 8-bit write cycle is identical to the first 8-bit write.  $\overline{\text{MBE}}$  stays true (low) during the entire (1.8 microseconds) cycle.

## I/O BUS LOADING

| SIGNAL         | TOTAL SWITCHING<br>LOAD (pF) | MAXIMUM PERIPHERAL<br>LOAD (pF) |

|----------------|------------------------------|---------------------------------|

| D0-D7          | 210                          | 90                              |

| A0A2           | 100                          | 90                              |

| A3-A14         | 100                          | 90                              |

| A15/CRUOUT     | 110                          | 100                             |

| <b>Ø</b> 3     | 110                          | 100                             |

| RESET          | 100                          | 90                              |

| READY          | 80                           | <b>7</b> 0                      |

| CRUIN          | 125                          | 90                              |

| <u>CRU</u> CLK | 100                          | 90                              |

| MBE            | 100                          | 90                              |

| WE             | 100                          | 90                              |

| SBE            | 35                           | 25                              |

| DBIN           | 100                          | 90                              |

| MEMEN          | 100                          | 90                              |

| HOLD           | 80                           | 70                              |

FIGURE C. I/O WRITE TIMING

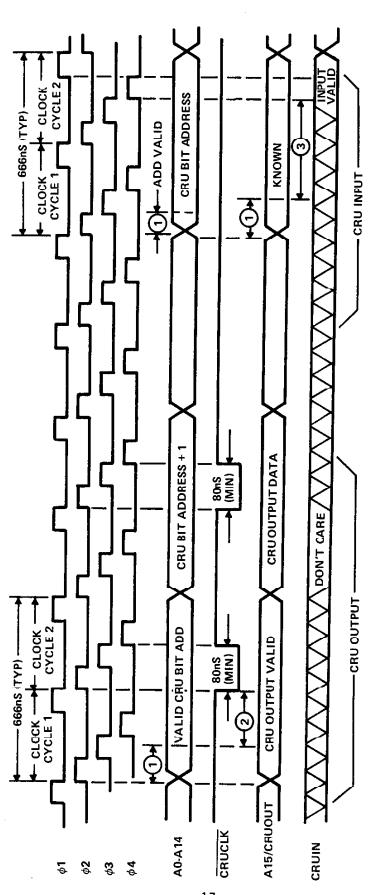

# CRU TIMING

CRU interface timing is shown in Figure D. The CRUOUT cycle is composed of two clock cycles. When placed on the address bus AO through A14, the CRU bit address is allowed to settle for 100 nanoseconds (min). CRUCLK is a 63 nanoseconds (max) low true signal which occurs on the trailing edge of \$\phi\$1 of clock cycle 2. CRUOUT data is valid at the start of clock cycle 1 and is latched by the CRUCLK in the respective peripheral.

CRUIN also consists of two clock cycles of 666 nanoseconds (TYP). Again 100 nanoseconds is allowed for the address bus to settle. The CPU samples the CRUIN line on the leading edge of  $\emptyset$ 1 of clock cycle 2. Data must be valid 40 nanoseconds (min) before that. This implies an access time of less than 400 nanoseconds for CRUIN.

(1) SETTLING TIME = 100nS (MIN)

(2) ADD VALID TO  $\overline{CRUCLK}$  = 233nS (TYP)

(3) ADD VALID TO VALID CRUIN = 400nS (MAX)

17

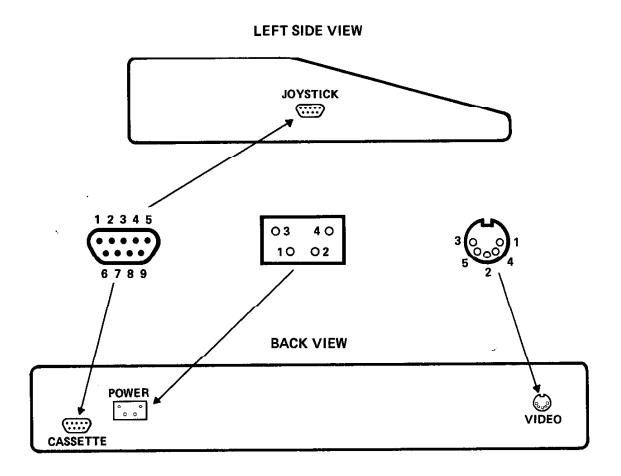

FIGURE E. CONNECTOR PIN IDENTIFICATION DIAGRAM

FIGURE G. TI-99/4A CONSOLE POWER SUPPLY

# SECTION B--INTERFACE CONSIDERATIONS

# B.1--CPU REQUIREMENTS

# **B.1.1** General Comments

The purpose of this section is to outline considerations necessary or advisable for hardware used for interfacing peripherals to the TI-99/4A.

Required TI-99/4A timing is shown on pages 12-17 in Section A of this manual, and Section D includes details concerning the software requirements for peripheral interfacing.

# B.1.2 TI-99/4A Memory Space Organization

The memory map of the TI-99/4A is as follows. The allocated spaces are shown in parentheses, and the actual memory space used is shown where applicable. This is notable of the memory-mapped devices (MMD) in the >8000 to >9FFF space. All of these devices reside in 1K blocks, and block decoding is used to select them. Even though they are shown to respond at the base address, they will respond ANYWHERE in the 1K block assigned to them. An example is the 256 byte SRAM which is decoded to respond at a base of >8000. This SRAM repeats at bases of >8100, >8200, and >8300, and software is written to conform to the >8300 base. Note that there is a given amount of space which cannot be used because of the basic space definition and the decoding used on existing products.

# B.1.2.1 READ Before WRITE Considerations

There are different READ and WRITE addresses for most of the memory-mapped devices (MMDs). This is because the TMS 9900 does a READ operation at the destination address prior to writing to it. Many of the MMDs have internal address registers that autoincrement after either a RFAD or a WRITE operation. This autoincrement characteristic of the MMD may not produce the desired results if it is not taken into consideration when designs or modifications are made.

The READ before WRITE exists because the 9900 is a word-oriented machine from a memory access standpoint. The several byte-oriented instructions are carried out by the machine in a word execution format, and the other byte in the word must not be altered. The machine itself must save the unaltered byte, concatenate the new byte with it, and return the word to memory. The internal logic of the TMS 9900 is designed this way because it was to the designers distinct advantage to do this same READ before WRITE on both byte and word moves.

# B.1.2.2 Cartridge Memory Space

The cartridge memory space at >6000 must be treated as if it is logically connected to the cartridge port. The GROM chips are rather poor line drivers at best, and their life on the I/O data bus is limited. Even though the GROM data bus is currently connected directly to the I/O data bus, there is no guarantee that updated versions of the TI-99/4A will have the same connection. The new generation TI console will probably isolate the GROM data bus from the I/O data bus. DON'T TRY TO ACCESS THE CARTRIDGE MEMORY SPACE FROM THE I/O PORT!

# TI-99/4A Memory Map

| !                                               |

|-------------------------------------------------|

| !>0000                                          |

| Console ROM (8K BY) >1FFF                       |

| >2000                                           |

| Used by 32K Mem Exp<br>(8K BY) >3FFF            |

| ·>4000                                          |

| DSR ROM Space<br>(8K BY) >5FFF                  |

| >6000                                           |

| Cartridge Memory Space<br>(8K BY) >7FFF         |

| >8000                                           |

| Console 256 byte RAM<br>(1K BY) >83FF           |

| >8400                                           |

| Sound Chip, 1 BY req'd<br>(1K BY) >87FF         |

| >8800                                           |

| VDP READ, 2 BY req'd<br>(1K BY) >8BFF           |

| >8COO<br>VDP WRITE, 2 BY req'd<br>(1K BY) >8FFF |

| >9000                                           |

| Speech Module READ Space (1K BY) >93FF          |

| >9400                                           |

| Speech Module WRITE Space :                     |

| (1K BY) >97FF                                   |

| >9800<br>GROM READ, 2 BY req'd<br>(1K BY) >9BFF |

| >9COO                                           |

| GROM WRITF, 2 BY req'd ! (1K BY) >9FFF !        |

| >A000<br>Used by 32K Mem Exp<br>(24K BY) >FFFF  |

|                                                 |

## B.1.3 CRU (Communications Register Unit) Space Definition

As with the memory space decoding, the CRU space devices are not fully decoded. Thus, most devices will respond just as well to other addresses in their block as they will to the block base address. By and large, the CRU space is allocated to peripherals with only a very small amount devoted to internal machine control (keyboard scan, cassette control, etc.).

#### B.1.3.1 Disallowed Instructions.

The control signal "CRUCLK" is also not fully decoded. Because the most-significant three address bus bits are not included in the decode, certain instructions of the TMS 9900 must be disallowed. These are: LREX, CKOF, CKON, RSET, and IDLE.

DO NOT USE THESE INSTRUCTIONS. THE LOGIC BLOCKS FED BY CRUCLK WILL INTREPRET THAT CLOCK SIGNAL AS A CRU OPERATION.

#### B.1.3.2 CRU OUTPUT Definition.

There is a single restriction on the definition of CRU DUTPUT bits for peripheral use: the base address bit. This bit must be used to "page in" DSR ROM's when SET, and should, where possible, be RESET by the Power-Up RESET line in the I/O Port. Thus, the DSR ROM will be "paged out" by a RESET operation. For more information, see the paragraph on DSR ROM CONSIDERATIONS.

## B.1.3.3 CRU INPUT Definition.

There is no definition for CRU Input lines, and one is free to define them within that peripheral space as desired.

#### B.1.3.4 Spare CRU Bit Use.

Spare CRU bits may be put to good use as test bits. If spare INPUT and OUTPUT bits are available, the ones used should be chosen so that spare INPUT's may be connected to spare OUTPUT's (each pair displaced by the same amount from the base) to form software FLAG bits. Otherwise, spare INPUTS bits should be tied to VCC or GROUND in some manner that will be verified during the power-up routine execution for that peripheral. Spare OUTPUT bits may be left unconnected or terminated on an etch pad to be connected to automatic test equipment. This is particularly useful when combined with signature test hardware and test software.

# CRU MAP

| !              |                                                |                      |

|----------------|------------------------------------------------|----------------------|

| >0000          | CPU TMS 9901 s<br>32 lines requi               | pace<br>red<br>>03FE |

| >0400          | Unassigned                                     | >OFFE                |

|                | test equipmen<br>n production l<br>(128 Lines) |                      |

| >1100          | Disk Controll<br>(128 Lines)                   | er<br>>11FE          |

| >1200          | Modem                                          | >12FE                |

| >1300          | Primary RS232                                  | >13FE                |

| >1400          | Unassigned                                     | >14FE                |

| >1500<br>Se    | econdary RS232                                 | >15FE                |

| >1 <b>6</b> 00 | Unassigned                                     | >16FE                |

| >1700<br>      | HEX-BUSTM                                      | >17FE                |

| >1800<br>      | Thermal Printer                                | >18FE                |

| >1900<br>EF    | PROM Programmen                                | >19FE                |

| <b></b>                                    |

|--------------------------------------------|

| >1A00<br>Unassigned<br>>1AFE               |

| >1B00<br>Unassigned<br>>1BFE               |

| >1COO Video Controller Card >1CFE          |

| >1D00<br>IEEE 488 Controller Card<br>>1DFE |

| >1E00<br>Unassigned<br>>1EFE               |

| >1F00<br>P-Code Card<br>>1FFE              |

# B.1.4 TI-99/4A Peripheral Polling

The TI-99/4A polls the I/O Port for the presence of peripherals on either a software restart or a hardware RESET. This polling starts in the CRU space at >1000, and continues in increments of >100 until >1F00 has been polled. Power-up routines will be executed for each peripheral as its DSR ROM is polled (if the DSR header indicates that a power-up sequence is required).

## B.1.5 Indicator LED

An indicator LED shall be provided, and shall be driven by a unique CRU OUTPUT bit. If all CRU OUTPUT bits have been defined, it shall be acceptable to connect the LED drive to the DSR ROM page bit. This LED provides visual feedback to the user that the peripheral card is present and active. All cards presently marketed by TI must provide this indicator. The LED is amber or yellow.

#### B.1.6 DSR ROM Considerations

The DSR ROMs for all peripherals must be based at >4000 and may be contiguous through >5FFF. These ROMs must not respond unless the respective CRU DSR ROM page bit is set ON (set to a high level with either a SBO instruction or "1" data in a LDCR instruction). It is the responsibility of the CPU to insure the proper control of all of the DSR ROM page bits.

# B.1.6.1 Extended DSR ROM Techniques.

ROM Space in excess of 8K bytes may be obtained by bringing sequential 8K blocks into the DSR ROM page. Secondary blocks (pages) may be placed anywhere in available TI-99/4A Memory Space. The secondary page bit may be obtained from the assigned CRU space to that peripheral (as was done on the P-Code PCB) or by writing to a ROM address and then decoding that condition to strobe a flip-flop. The latter method was used on the Extended Basic cartridge to page the upper 4K half of that space. Either a data bus or an address bus bit may be used for data to the FF. Both schemes provided a nonpaged 4K base ROM, and paged the upper 4K half of the space.

#### **B.2-EXPANSION UNIT REQUIREMENTS**

#### B.2.1 System Bus Requirements

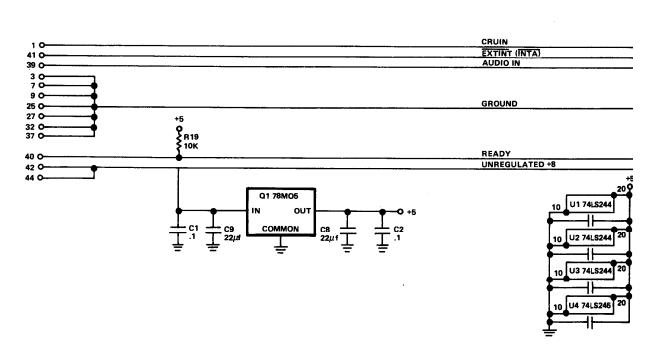

There are only two design considerations that must be understood to interface with the system bus. One controls a Data Bus driver on the TI-99/4A end of the connecting cable, and the other is used during printed circuit board (PCB) burn-in.

#### B.2.1.1 Remote Data Bus Driver.

As has been previously noted, there are additional requirements for interfacing through the Peripheral Expansion Unit (PFU). Regardless of the processor driving the PEU, a signal must be provided to indicate to the interface that a memory cycle is being requested for a PCB in the PEU. This signal is termed "RDBENA\*", and is used to enable Data Bus drivers on the TI-99/4A end of the cable. It must function as an open-collector signal, but a tri-state gate may be used instead if the input is grounded and the tri-state controller is connected in parallel with that gate for the Data Bus Buffer.

#### B.2.1.2 Burn-In Consideration.

A single high true line shall be provided to enable the PCB to respond to both memory and CRU accesses. This line is held at a high level in the PEU, but is driven to allow a parallel connection of 16 PCBs during burn-in. When low, this signal shall disable the PCB from driving any of the system memory and CRU bus lines. The interrupt sensing has been excepted from this in the past.

## **B.2.2** Power Allocation Assumptions

The following is a guide for maximum load current a PCB should present to the PEU.

- o 250 ma on the +15v unregulated bus.

- o 500 ma on the +8v unregulated bus.

- o 30 ma on the -15v unregulated bus.

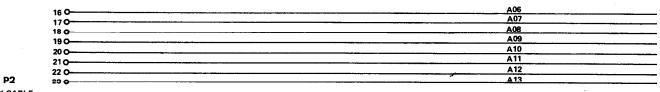

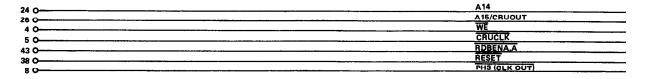

# B.2.3 System Bus Pin Definition

# .100" PIN TO PIN SPACING, ATTLEBORO CONNECTOR

| PIN NO.                                                                                | MNEMONIC                                                             | FUNCTION                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9                                              | GND<br>READY A<br>GND<br>RESET*<br>GND<br>SCLK<br>LCP*               | +5v 3-T Regulator supply voltage<br>+5v 3-T Regulator supply voltage<br>Logic Ground<br>System READY<br>Logic Ground<br>Active LOW system-driven RESET<br>Logic ground<br>System clock<br>Second generation CPU indicator.                                                          |

| 10<br>11                                                                               | AUDIO<br>RBDENA*                                                     | O=Second generation CPU; 1=TI-99/4<br>Input audio<br>Active LOW remote data bus driver                                                                                                                                                                                              |

| 12<br>13                                                                               | PCBEN<br>HOLD*                                                       | Enable control line<br>Active HIGH PCB enable for burn-in<br>Active LOW CPU HOLD request                                                                                                                                                                                            |

| 14                                                                                     | IAQHA                                                                | Second generation CPU only<br>IAQ HOLDA logical OR                                                                                                                                                                                                                                  |

| 15<br>16                                                                               | SENITR*                                                              | Second generation CPU only Interrupt Level A Sense Enable Interrupt Level B Sense Enable                                                                                                                                                                                            |

| 17<br>18                                                                               | INTA*<br>LOAD*                                                       | Second generation CPU only Active LOW Interrupt Level A Low for TI-99/4 Memory Expansion, High for linear memory space. Second generation CPU only.                                                                                                                                 |

| 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33 | D7 GND D5 D6 D3 D4 D1 D2 GND D0 A14.A A15/CRUOUT.A A12.A A13.A A10.A | TMS9900 LOAD* input System DATA Bus, LSB Logic Ground System DATA Bus Logic Ground System DATA Bus, MSB Address Bit Address Bit Address Bit Address Bit Address Bit |

# System Bus Pin Definition (Continued)

| PIN NO. | MNEMONIC  | FUNCTION                          |

|---------|-----------|-----------------------------------|

| 34      | A11.A     | Address Bit                       |

| 35      | A08.A     | Address Bit                       |

| 36      | A09.A     | Address Bit                       |

| 37      | A06.A     | Address Bit                       |

| 38      | A07.A     | Address Bit                       |

| 39      | A04.A     | Address Bit                       |

| 40      | A05.A     | Address Bit                       |

| 41      | A02.A     | Address Bit                       |

| 42      | A03.A     | Address Bit                       |

| 43      | A00.A     | Address Bit                       |

| 44 -    | A01.A     | Address Bit                       |

| 45      | AMB.A     | Address Bit, normally HIGH        |

| 46      | AMA.A     | Address Bit, normally HIGH        |

| 47      | GND       | Logic Ground                      |

| 48      | AMC.A     | Address Bit, MSB normally HIGH    |

| 49      | GND       | Logic Ground                      |

| 50      | CLKOUT*   | Active LOW CPU CLOCK              |

| 51      | CRUCLK.A* | Active LOW CRU Output Clock       |

| 52      | DBIN.A    | Data Bus Dir'tn, HIGH is CPU READ |

| 53      | GND       | Logic Ground                      |

| 54      | WE.A*     | LOW true CPU Write Enable-        |

| 55      | CRUIN     | HIGH true CRU Input data          |

| 56      | MEMEN.A*  | Active LOW memory request         |

| 57      |           | -12v 3-T Regulator supply voltage |

| 58      |           | -12v 3-T Regulator supply voltage |

| 59      |           | +12v 3-T Regulator supply voltage |

| 60      |           | +12v 3—T Regulator supply voltage |

# B.3--DESIGN AND DEVELOPMENT REQUIREMENTS

This listing covers both hardware and PCB design rules.

- o Each PCB must be completely disabled by an active low disable (active high enable). The disable must disable both memory and CRU functions on the PCB and is used for burn-in purposes.

- n The  $\pm 12v$ ,  $\pm 5v$ , and  $\pm 12v$  power etches shall be double spaced from other etches where possible. This minimizes a TTL to power line short or a power etch to power etch short.

- o Signals such as CRUIN that are taken very far from the system I/O connector shall be guarded with GROUND etch. Where practical, these signals should be buffered with tri-state buffers.

- o Buffers to drive the bus must be physically close to the I/O Bus. The prototyping PCBs have most of this already in place, but signals such as READY and CRUIN do not have them because they are not always used. A connection to the system bus constitutes a stub connection, which generally obeys transmission line theory. These stubs should be kept as short as is practical.

- o All 19 system address bits shall be included in the memory space decode for that peripheral. Assume AMC, AMB, and AMA to be in the high state.

- o Address lines A00 through A07 shall be included in the CRU Space decode even though the TI-99/4A assumes A00 thru A02 to be zero.

- There are two levels on which to interrupt, but the TI-99/4A supports only one (INTA\*). THIS IS THE ONE YOU MUST USE. Interrupt level status bits are defined by the Personal Computer PCC at Texas Instruments, and for the moment are not sensed by the TI-99/4A. If they were to be sensed, the TI-99/4A would cause a line to go low (SENILA\*), which tells the PCB logic to gate its status bit to the system data bus.

- As a design aid, the Personal Computer Group has available a prototyping printed circuit board (PCB). This PCB will accommodate about 36 16-pin DIP sockets, and has the necessary system bus buffers in place with etch connections to the system I/O pins. The PCB designer need only to hook the buffered signal to his logic design. Schematics of this PCB are available (TI part number 1039334) and standard TI-99/4A timing diagrams should be used for the PEU PCB Design.

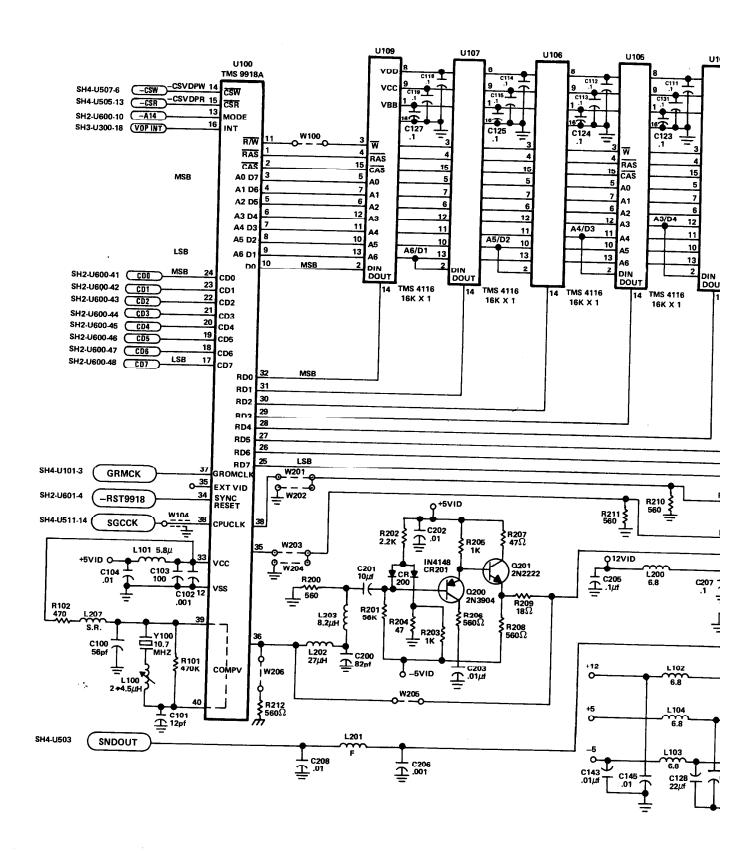

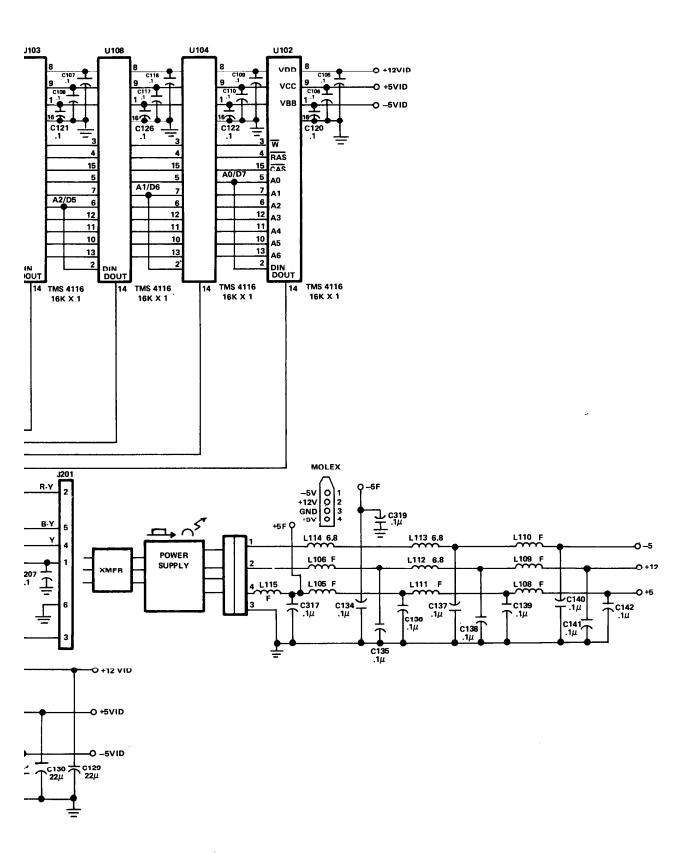

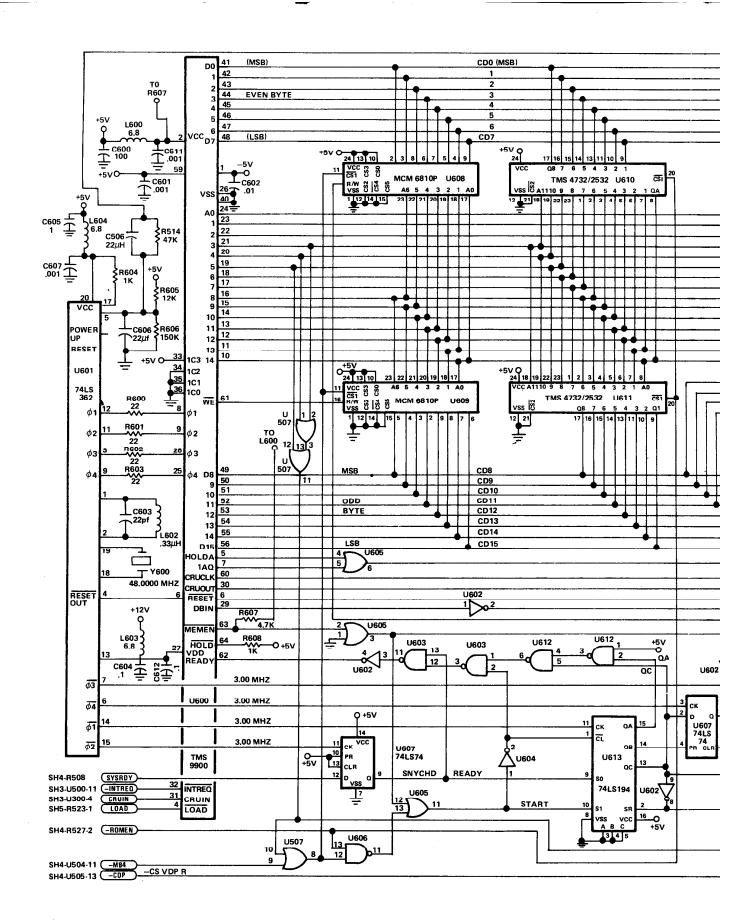

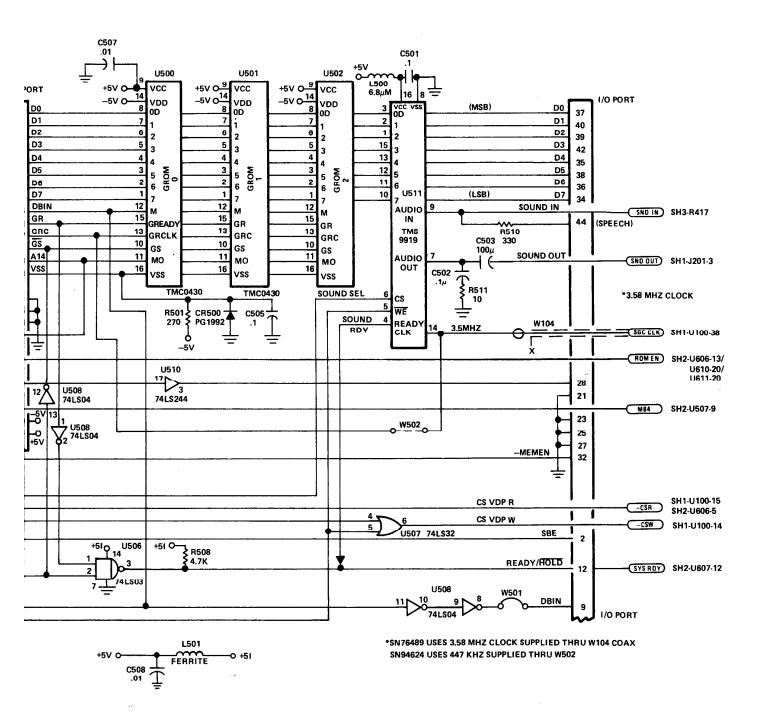

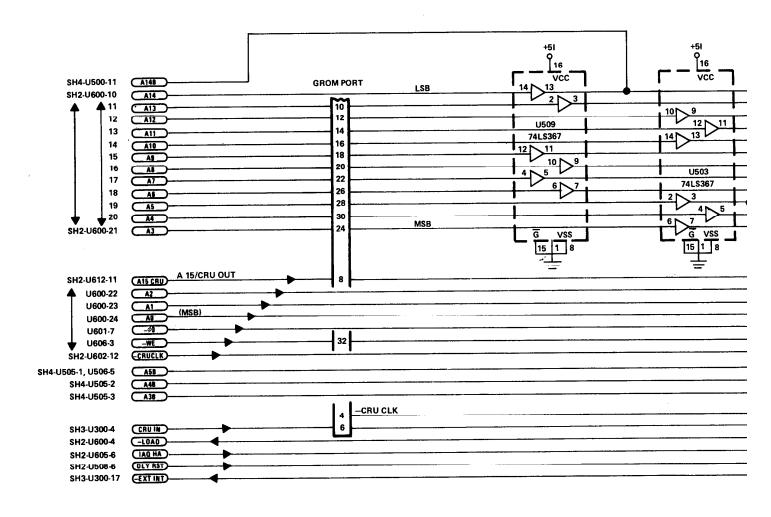

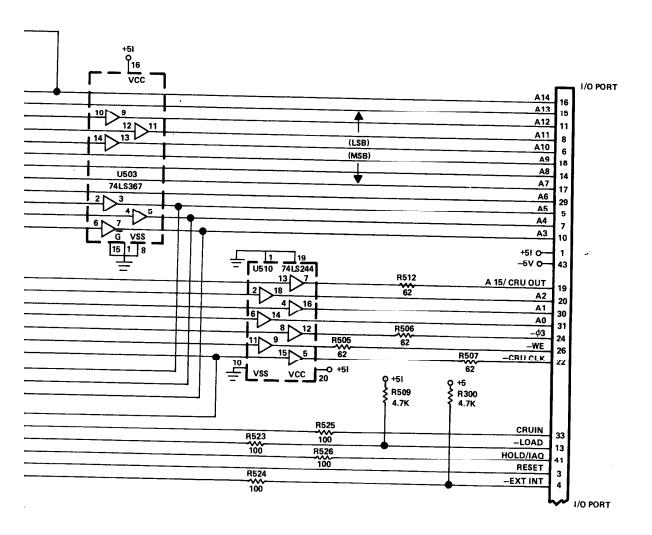

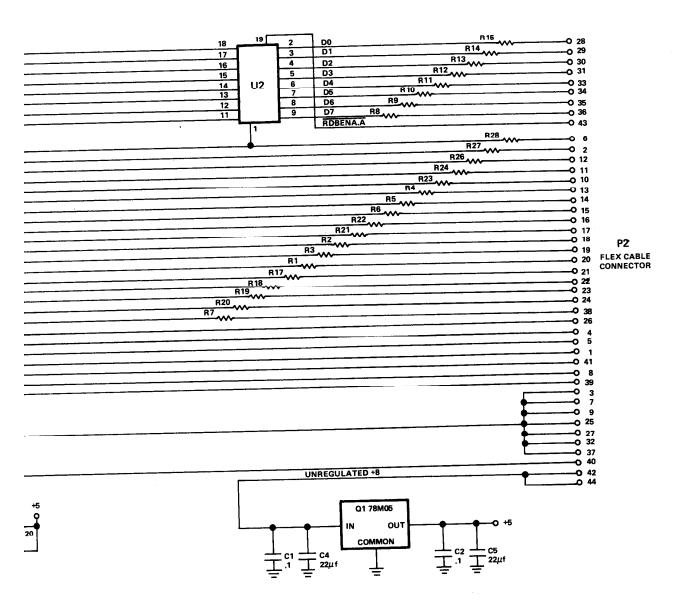

PERIPHERAL EXPANSION UNIT SCHEMATIC DIAGRAM

#### Section C--FILE MANAGEMENT SPECIFICATIONS

#### C.1 Introduction

This document contains a complete specification for the file management system of the TI-99/4A Home Computer.

The text in this document has been completely revised to reflect changes that have been made to facilitate new options in the TI-99/4A Home Computer.

The TI-99/4A Home Computer will support all file features described in this document. Some minor additions have been made concerning the status (C.3.2.10) and the error code section (C.3.4) to reflect changes for the TI-99/4A Disk Peripheral. These changes do not affect any DSR that currently exists.

Section C.4.3 has been provided to give information to the GPL applications programmer on how to access DSRs and for the peripheral programmer on how the information is passed on a DSR.

## C.2 I/O Handling

The approach used in the TI-99/4A Home Computer File Management System has been that all devices should look the same to an application program. Therefore when peripherals are added to the computer, it should not affect the BASIC interpreter. Only the peripheral driver (Device Service Routine, or DSR) will have to be added to the software.

All peripherals for the TI-99/4A Home Computer, with the exception of the keyboard/display, are considered equivalent by an application program, within physical limitations (reading data from a thermal printer is clearly impossible). These physical limitations are determined in the device service routine and returned to the application program as an error condition.

The TI-99/4A Home Computer File Management System supports both random and sequential access files. Both file types use the same supervisor call mechanism in order to insure a high degree of device independence. Hardware devices (such as a line printer) are accessed as sequential files except that no file name is appended to the device name.

The following sections describe the file structures available to the BASIC interpreter, how to create and delete files, and how to perform file I/O.

Two different kind of file organizations are supported:

- o Sequential files

- o Relative record files (random access)

#### C.2.1 File Organization and Use

The following paragraphs discuss the file organization and use for each of the two file types.

#### C.2.1.1 Sequential Files

Sequential files are both used for disk-based files and for I/O to other devices. They consist of fixed or variable record length files whose records are always accessed serially, like the output to the thermal printer.

#### C.2.1.2 Relative Record Files

Relative record files are also called random access files because, unlike a sequential file, records may be accessed in an arbitrary order. Therefore relative record files can only be supported on random access media such as floppy disks.

The records within a relative record file are addressed by a unique record number. To access record X, the value X has to be placed in the appropriate field of the I/O Peripheral Access Block. The range of record numbers is from zero to one less than the number of records in the file. Records in a relative record files are a fixed length, specified at file creation.

Records in a relative record file can also be accessed in a sequential way by specifying only the first record in the sequence. The supervisor then automatically updates the record number each time after a record has been read.

# C.2.2 File Management Overview

# C.2.2.1 Terminology

A file consists of a collection of data groupings called logical records. This division of the file into logical records does not necessarily correspond to the physical division of data on the medium (like a sector on a disk). Thus there are two types of records:

- Logical records—The data grouping of a file as seen by an application program.

- Physical records—The buffers physically transferred between memory and medium.

Relative file I/O from a program is done on a logical record with a fixed length. This enables the system to compute the actual location of any logical record relative to the beginning of file.

Sequential files allow both fixed and variable length records.

When a file is created, the logical record size must be specified. For relative record files this size must be exact. For sequential files the specification indicates an upper limit for the size of a variable record, or the exact length of a fixed-length record. In case a zero is specified for either filetype, the DSR must select a default for the record size.

The physical record size for any medium is specified within the DSR and is implementation dependent.

#### C.2.2.2 File-Type Attribute

The file-type attribute specifies the format in which the data in the file is represented. The two file types are:

- O DISPLAY-Displayable or printable character strings.

Each data record corresponds to one print line.

- o INTERNAL-Data in INTERNAL machine format.

The file-type attribute is internal to the application program. It is merely stored and passed on by the DSR as a distinction between two data types, without affecting the actual data stored.

#### C.2.2.3 Mode of Operation

A file is opened for a specific mode of operation, specified in the OPEN I/O call. The four modes of operation are:

- o INPUT The contents of the file may be read, but may not be altered.

- OUTPUT The file is being created. Its contents may be written but not read.

- o UPDATE The contents of the file may be both written and read. Note that this mode of operation is only be supported by random access devices.

- O APPEND New data may be added at the end of the file, but the contents of the file may not be read

Each DSR decides whether or not a specific mode for an I/O operation can be accepted by the corresponding device.

#### C.2.2.4 Temporary Files

In the subsets of TI standard BASIC used for the TI-99/4A Home Computer, the file-life attribute is not implemented. Therefore there is no need for the File Management System to support temporary files, and all files are permanent by definition.

## C.3 Implementation

As mentioned in section C.2, the DSRs should present a uniform interface between the File Management System and the peripherals. This section will give details about implementing this interface.

## C.3.1 Peripheral Access Block Definition

All DSRs are accessed through a Peripheral Access Block (PAB). The definition for the PAB is the same for every peripheral. The only difference between peripherals, as seen by any application program, is that some peripherals will not support every option provided for in the PAB.

All PAB's are physically located in VDP RAM. They are created before the OPEN call and are not to be released until the I/O has been closed for that device or file.

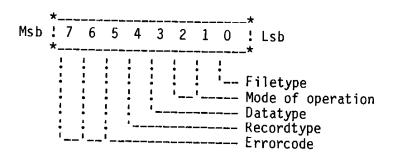

Figure C.3.1.1 shows the layout of a PAB. The PAB has a variable length, depending upon the length of the file descriptor.

The meaning of the bytes and bits within the PAB is explained below.

| Byte | Bit |              | Meaning                                                                                                              |                          |

|------|-----|--------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|

| 0    | -   | I/O opcode   | Contains opcode for the curr call. A description of the are given in section C.3.2.                                  | ent I/O<br>valid opcodes |

| 1    | -   | Flagbyte/sta | tus All the information the about file-type, mode of ope data-type is stored in this meaning of the bits within tis: | ration, and<br>byte. The |

| Byte | Bit | Meaning                                                                                                                                                                                                                                                     |

|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 0   | FiletypeIndicates file-type.                                                                                                                                                                                                                                |

|      |     | <pre>0 = Sequential file 1 = Relative record file</pre>                                                                                                                                                                                                     |

|      | 1,2 | Mode of operationIndicates operation mode for which file has been opened.                                                                                                                                                                                   |

|      |     | OO = UPDATE<br>O1 = OUTPUT<br>10 = INPUT<br>11 = APPEND                                                                                                                                                                                                     |

|      | · 3 | DatatypeIndicates type of data stored in the file.                                                                                                                                                                                                          |

|      |     | <pre>0 = DISPLAY type data 1 = INTERNAL type data</pre>                                                                                                                                                                                                     |

|      | 4   | RecordtypeIndicates type of record used.                                                                                                                                                                                                                    |

|      |     | <pre>0 = Fixed length records 1 = Variable length records</pre>                                                                                                                                                                                             |

|      | 5–7 | Error code—These three bits indicate, in combination with the $I/O$ opcode, the error type that has occurred (0 = no error).                                                                                                                                |

| 2,3  | _   | Data buffer address—Address of the data buffer the data has to be written to or read from.                                                                                                                                                                  |

| 1    | _   | Logical record lengthIndicates the logical record length for fixed length records, or the maximum length for a variable length record (see flagbyte).                                                                                                       |

| 5    | -   | Character count—Number of characters to be transferred for a WRITE opcode, or the number of bytes actually read for a READ opcode (not equivalent to INPUT and OUTPUT mode).                                                                                |

| 6,7  | -   | Record number—Only required if the file opened is of the relative record type. Indicates the record number the current I/O operation is to be performed upon (this limits the range of record numbers 0-32767). The highest bit will be ignored by the DSR. |

| Byte | Bit | Meaning                                                                                                              |

|------|-----|----------------------------------------------------------------------------------------------------------------------|

| 8    | _   | Screen offset—Offset of the screen characters in respect to their normal ASCII value.                                |

| 9    | -   | Name length——Length of the file descriptor following the PAB.                                                        |

| 10+  | -   | File descriptor—Device name and, if required, the filename and options. The length of this descriptor is given in 9. |

| O I/O OPCODE               | ! 1 FLAG / STATUS        | _ |

|----------------------------|--------------------------|---|

| 2,3<br>DAIA BUFFE          | RADDRESS                 |   |

| 4<br>LOGICAL RECORD LENGTH | : 5<br>: CHARACTER COUNT |   |

| 6,7<br>R E C O R D         | N U M B E R              |   |

| 8<br>SCREEN OFFSET         | 9 NAME LENGTH            |   |

| 10                         |                          | - |

Figure C.3.1.1 PAB Layout

## C.3.2 I/O Opcodes

This section describes the valid opcodes that can be used in a PAB. These valid opcodes are shown in Figure C.3.2.1.

The following section will describe the general actions invoked by an I/O call with each of the I/O opcodes. Each I/O call returns any error codes in the FLAG/STATUS byte of the PAB.

| 0pcode | Meaning        |

|--------|----------------|

| 00     | OPEN           |

| 01     | CLOSE          |

| 02     | READ           |

| 03     | WRITE          |

| 04     | RESTORE/REWIND |

| 05     | LOAD           |

| 06     | SAVE           |

| 07     | DELETE         |

| 08     | SCRATCH RECORD |

| 09     | STATUS         |

Figure C.3.2.1 I/O Opcodes

#### C.3.2.1 OPEN

The OPEN operation should be performed before any data transfer operation except LOAD or SAVE. The file remains open until a CLOSE operation is performed. The mode of operation for which the file has to be opened should be indicated in the flagbyte of the PAB. In case this mode is UPDATE, APPEND, or INPUT, the record length will be returned in byte four. Any given non-zero record length will be checked against this stored length. For OUTPUT the record length can be specified, or a default can be used by specifying record length zero.

For any device, an OPEN operation must be performed before any other I/O operation. The DSR need only check the record length and I/O mode on an OPEN. Changing I/O modes after an OPEN may cause unpredictable results.

#### C.3.2.2 CLOSE

The CLOSE operation informs the DSR that the current I/O sequence to that DSR has been completed.

After the CLOSE operation, the space allocated for the PAB may be used for other purposes. As long as a PAB is connected to an active device, the contents of that PAB must be preserved.

If file or device is opened for OUTPUT or APPEND mode, an EOF (end of file) record is written to the device or file before disconnecting the PAB.

#### C.3.2.3 READ

The READ operation reads a record from the selected device and copies the bytes in the specified buffer. The buffer address is specified in PAB entry 2 and 3; the buffer size is specified in PAB entry 4. The actual number of characters stored is returned in PAB entry 5 (CHARACTER COUNT). If the length of the input record exceeds the buffer size, the remaining characters will be discarded.

#### C.3.2.4 WRITE

The WRITE operation writes a record from the buffer specified in the PAB to the specified device. The number of bytes to be written is specified in byte five of the PAB.

#### C.3.2.5 RESTORE/REWIND

The RESTORE/REWIND operation repositions the file READ/WRITE pointer either to the beginning of the file, or, in the case of a relative record file, to the record specified in bytes six and seven of the PAB.

A RESTORE can only be used if the file is opened for INPUT or UPDATE mode. For relative record files, a RESTORE could be simulated in any I/O mode by specifying the record at which the file has to be positioned in bytes six and seven of the PAB. The next I/O operation then automatically uses the indicated record.

#### C.3.2.6 LOAD

The LOAD operation loads an entire memory image from an external device or file into VDP RAM. All the control information the application program needs should be concatenated to the program image. No intermediary buffers are used. The entire memory image is dumped starting at the specified location.

The LOAD operation is a stand-alone operation, i.e. the LOAD operation is used without a previous OPEN operation.

For the LOAD operation, the PAB needs to contain the following information:

Bytes 2,3--Start address of the memory dump area

Bytes 6,7--Number of bytes available.

Aside from the I/O opcode and the file descriptor, no other PAB entry is required for a LOAD operation.

#### C.3.2.7 SAVE

SAVE is the complementary operation for LOAD. It is used for writing memory images to a device or file. All necessary control information should be linked to the memory image, so that the information plus program image use on contiguous memory area. Again, only a small part of the PAB is used. Aside from the usual information (I/O opcode and file descriptor), the PAB contains:

Bytes 2,3--Start address of the memory area

Bytes 6.7--Number of bytes to be saved.

#### C.3.2.8 DELETE

The DELETE operation deletes the specified file from the specified device. This operation also CLOSEs the I/O sequence.

#### C.3.2.9 SCRAICH RECORD

The SCRATCH RECORD operation scratches the specified record from the specified relative record file. The record to be scratched is specified in bytes six and seven of the PAB. This operation will cause an error for sequential files and devices. This operation is not currently supported by any device.

#### C.3.2.10 STATUS

This information can be asked for at any time, although some information is only meaningful if a file has been opened for access.

To indicate the current status of the file, byte eight (SCREEN OFFSET) is used. Upon the DSR call byte eight should contain the usual screen characters base address. The DSR can use only this byte and is guaranteed not to destroy any other entry in the PAB.

The meanings of the bits within byte eight after return from the DSR are:

- O Logical end of file. If this bit is set, the file is at the end of its previously created contents. This is usually the case if the file has been opened for APPEND mode. Depending upon the mode of operation for which the file has been opened, data can still be written to the file (APPEND, OUTPUT or UPDATE mode). However, a "read" operation will cause an ATTEMPT TO READ PAST EOF error to occur.

- Physical end of file. If set, no more data can be written, since the physical limits of the device have been reached. Generally this means an end of medium has been detected on the device.

- Record type. If set, the record type is VARIABLE length. If cleared the record type is FIXED length.

- Filetype. If set, the file is a program file. If cleared, the file is a data file.

- Data type. If set, the data type is binary (INTERNAL). If cleared the data type is ASCII (DISPLAY) or file is program file.

- Reserved for the future use. Fixed to zero in the current peripherals.

- 6 PROTECT flag. If set, the file is protected against modifications. If cleared, the file is not protected.

- 7 File requested does not exist. A device will not set this bit, which means that on a device, any file exists.

Bits two--seven are valid if the file has not previously been opened. Bits zero and one can only be used for files that are currently opened for access. A file that is not currently open for access should indicate a zero in these two bits.

## C.3.3 Error Codes

The File Management System supports a number of error codes. They are:

| Error | ·                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Code  | Meaning                                                                                                                                        |

| 0     | Bad device name; the device indicated is not in the system.                                                                                    |

| 1     | Device is write protected.                                                                                                                     |

| 2     | Bad open attribute such as incorrect file type, incorrect record length, incorrect I/O mode, or no records in a relative record file.          |

| 3     | Illegal operation; i.e. an operation not supported on the peripheral or a conflict with the OPEN attributes.                                   |

| 4     | Out of table or buffer space on the device.                                                                                                    |

| 5     | Attempt to read past the end of file. When this error occurs, the file is closed. Also given for non-extant records in a relative record file. |

| 6     | Device error. Covers all hard device errors such as parity and bad medium errors.                                                              |

| 7     | File error such as program/data file mismatch, non-existing file opened in INPUT mode, etc.                                                    |

#### C.4 DSR Operations

This section describes how a variety of DSRs should react on the different I/O calls. It also discusses detailed software operations descriptions such as available registers and memory.

#### C.4.1 DSR Actions and Reactions

In the Home Computer File Management System, several assumptions are made about the way in which DSRs should react on conditions such as errors, special I/O modes, defaults, etc. This section is intended to explain the reactions of a DSR on these conditions.

#### C.4.1.1 Error Conditions

#### C.4.1.1.1. Non-existing DSRs

If a non-existing DSR is called by an application program, the File Management System will automatically return with the COND bit set. In this case, no DSR has actually been called, so the error code will show no errors.

The DSR search mechanism of the File Management System takes care of searching for the requested DSR. It tries to match the file descriptor to the DSR entries in the system. The matching algorithm matches the end of the descriptor, or the first period, whichever comes first. This enables the applications program to add special information for the DSR in the file descriptor, such as filename, BAUD-rate, print-width, character set, etc.

#### C.4.1.1.2 DSR-detected Errors

DSR-detected errors (see section C.3.4) should be indicated in the flag byte of the PAB. It is the application program's responsibility to clear this flag byte before every I/O call, and check it after the I/O call. This type of error is NOT indicated with the COND bit.

The DSR may provide additional information about the error type in the I/O opcode byte, although it is good practice not to destroy the least significant four bits of this byte, since they specify the I/O call.

At no time should the DSR use bits zero—four of the flagbyte for error indication, since these bits might contain vital system information about the file device.

## C.4.1.2 Special I/O Modes